# 32-Bit RISC Microprocessor TX19 Family TMP1962F10AXBG

## 1. Features

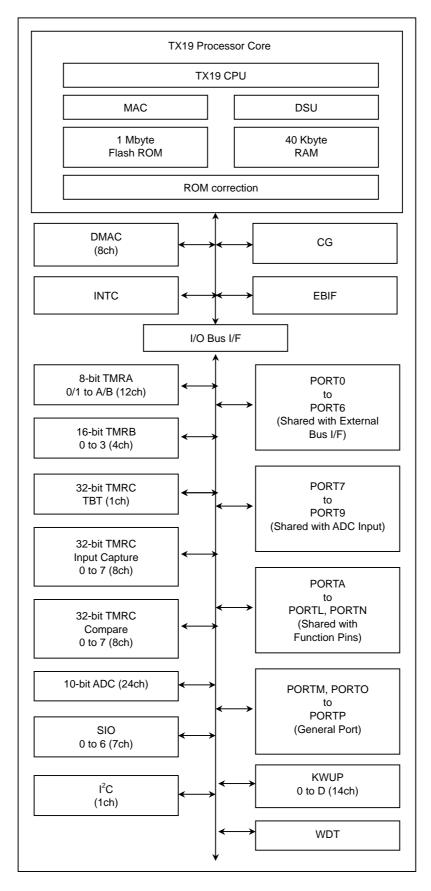

The TX19 is a family of high-performance 32-bit microprocessors that offers the speed of a 32-bit RISC solution with the added advantage of a significantly reduced code size of a 16-bit architecture. The instruction set of the TX19 includes as a subset the 32-bit instructions of the TX39, which is based on the MIPS R3000A<sup>TM</sup> architecture. Additionally, the TX19 supports the MIPS16 Application-Specific Extensions (ASE) for improved code density.

The TMP1962 is built on a TX19 core processor and a selection of intelligent peripherals. The TMP1962 is suitable for low-voltage and low-power applications.

Features of the TMP1962 include the following:

- (1) TX19 core processor

- 1) Two instruction set architecture (ISA) modes: 16-bit ISA for code density and 32-bit ISA for speed

- The 16-bit ISA is object-code compatible with the code-efficient MIPS16 ASE.

- The 32-bit ISA is object-code compatible with the high-performance TX39 family.

- 2) High performance combined with low power consumption

- High performance

- Single clock cycle execution for most instructions

- 3-operand computational instructions for high instruction throughput

- 5-stage pipeline

- On-chip high-speed memory

- DSP function: Executes 32-bit x 32-bit multiplier operations in a single clock cycle.

- · The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

<sup>030619</sup>EBP

- Low power consumption

- Optimized design using a low-power cell library

- Programmable standby modes in which processor clocks are stopped

- 3) Fast interrupt response suitable for real-time control

- Distinct starting locations for each interrupt service routine

- Automatically generated vectors for each interrupt source

- Automatic updates of the interrupt mask level

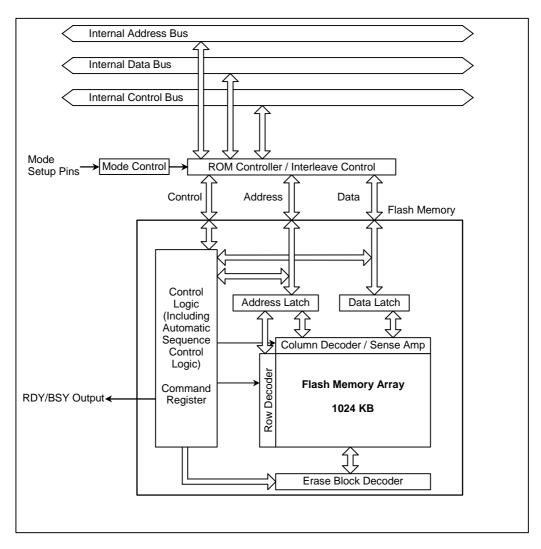

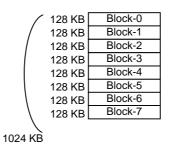

- (2) On-chip ROM/RAM

| Product        | On-chip ROM     | On-chip RAM |

|----------------|-----------------|-------------|

| TMP1962C10BXBG | 1 Mbyte         | 40 kbyte    |

| TMP1962F10AXBG | 1 Mbyte (Flash) | 40 Kbyte    |

|                |                 |             |

Collection function on ROM (8 words x 8 blocks)

- (3) External memory expansion

- 16-Mbyte off-chip address space for code and data

- External bus interface with dynamic bus sizing for 8-bit and 16-bit data ports (Separate bus/multiplex bus)

- (4) 8-channel DMA controller

- Interrupt- or software-triggered

- DMA transfers between on-chip or external memory and I/O module

- (5) 12-channel 8-bit timer

- 8-bit/16-bit/24-bit/32-bit interval timer mode

- 8-bit PWM mode

- 8-bit PPG mode

- (6) 4-channel 16-bit timer

- 16-bit interval timer mode

- 16-bit event counter mode

- 16-bit PPG output

- Input capture function

- 2-channel dual input counter function

- (7) 32-bit input capture

- 8-channel 32-bit input capture register

- 8-channel 32-bit compare register

- 1-channel 32-bit time base timer

- (8) 7-channel general-purpose serial interfaceEither UART mode or synchronous transfer mode can be selected.

- (9) 1-channel serial bus interface

Either I<sup>2</sup>C bus mode or clock-synchronous mode can be selected.

- (10) 24-channel 10-bit A/D converter (with internal sample/hold)

- External trigger start function

- Fixed channel/scan mode

- Single/repeat mode

- Timer monitor function

- (11) Watchdog timer

- (12) 4-channel chip select/wait controller

- (13) Interrupt sources

•

- 4 CPU interrupts: software interrupt instruction

- 55 internal interrupts: 7 priority levels, with the exception of the watchdog timer interrupt

- 25 external interrupts: 7 priority levels, with the exception of the NMI interrupt

1 used for an interrupt source and 14 used for KWUP

#### (14) 202-pin input/output ports

- (15) Four standby modes

- IDLE (HALT, DOZE), STOP

#### (16) Clock generator

- On-chip PLL (x3)

- Clock gear: Divides the operating speed of the CPU by 1/2, 1/4 or 1/8

(17) Endian ..... Bi-Endian

Big-endian

| Higher address | 31 24 | 23 16 | 15 8 | 7 0 | Word address |

|----------------|-------|-------|------|-----|--------------|

| ↑              | 8     | 9     | 10   | 11  | 8            |

|                | 4     | 5     | 6    | 7   | 4            |

|                | 0     | 1     | 2    | 3   | 0            |

Lower address

Byte 0 is the most significant byte (MSB) (bits 31-24)

The address of a word data item is the address of its MSB (byte 0).

Little-endian

| Higher address | 31 24 | 23 16 | 15 8 | 7 0 | Word address |

|----------------|-------|-------|------|-----|--------------|

| 1              | 11    | 10    | 9    | 8   | 8            |

|                | 7     | 6     | 5    | 4   | 4            |

|                | 3     | 2     | 1    | 0   | 0            |

Lower address

Byte 0 is the least significant byte (LSB) (bits 7-0)

The address of a word data item is the address of its LSB (byte 0).

(18) Operating frequency

40.5 MHz (Vcc = 2.2 V to 2.7 V)

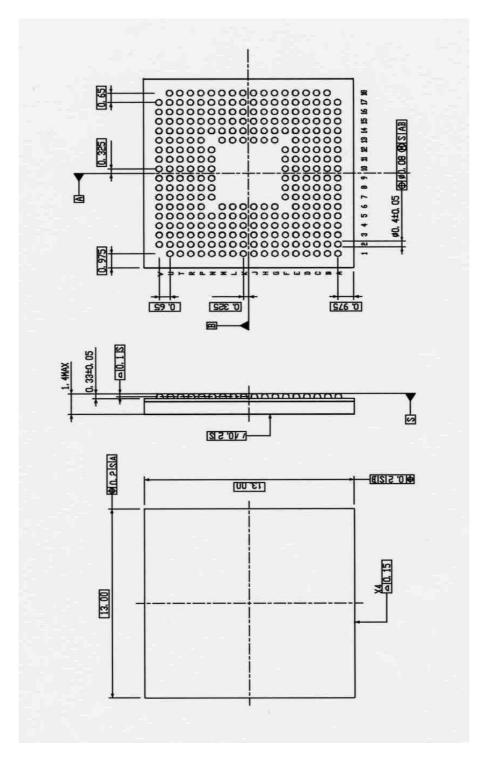

(19) Package

P-FBGA281 (13 x 13 x 0.65 mm pitch)

Figure 1.1 TMP1962F10AXBG Block Diagram

# 2. Pin Assignment

This section contains pin assignments for the TMP1962F10AXBG as well as brief description of the TMP1962F10AXBG input and output signals.

## 2.1 Pin Assignment

| The following illustrates the TMP1962F10AXBG pin assignment | ient. |

|-------------------------------------------------------------|-------|

|-------------------------------------------------------------|-------|

| A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 |     |

|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8 | B9 | B10 | B11 | B12 | B13 | B14 | B15 | B16 | B17 | B18 |

| C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | C11 | C12 | C13 | C14 | C15 | C16 | C17 | C18 |

| D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 |

| E1 | E2 | E3 | E4 | E5 | E6 | E7 | E8 | E9 | E10 | E11 | E12 | E13 | E14 | E15 | E16 | E17 | E18 |

| F1 | F2 | F3 | F4 | F5 |    | F7 | F8 | F9 | F10 | F11 | F12 |     | F14 | F15 | F16 | F17 | F18 |

| G1 | G2 | G3 | G4 | G5 | G6 |    |    |    |     |     |     | G13 | G14 | G15 | G16 | G17 | G18 |

| H1 | H2 | H3 | H4 | H5 | H6 |    |    |    |     |     |     | H13 | H14 | H15 | H16 | H17 | H18 |

| J1 | J2 | J3 | J4 | J5 | J6 |    |    |    |     |     |     | J13 | J14 | J15 | J16 | J17 | J18 |

| K1 | K2 | K3 | K4 | K5 | K6 |    |    |    |     |     |     | K13 | K14 | K15 | K16 | K17 | K18 |

| L1 | L2 | L3 | L4 | L5 | L6 |    |    |    |     |     |     | L13 | L14 | L15 | L16 | L17 | L18 |

| M1 | M2 | М3 | M4 | M5 | M6 |    |    |    |     |     |     | M13 | M14 | M15 | M16 | M17 | M18 |

| N1 | N2 | N3 | N4 | N5 |    | N7 | N8 | N9 | N10 | N11 | N12 |     | N14 | N15 | N16 | N17 | N18 |

| P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | P17 | P18 |

| R1 | R2 | R3 | R4 | R5 | R6 | R7 | R8 | R9 | R10 | R11 | R12 | R13 | R14 | R15 | R16 | R17 | R18 |

| T1 | T2 | Т3 | T4 | T5 | T6 | T7 | T8 | Т9 | T10 | T11 | T12 | T13 | T14 | T15 | T16 | T17 | T18 |

| U1 | U2 | U3 | U4 | U5 | U6 | U7 | U8 | U9 | U10 | U11 | U12 | U13 | U14 | U15 | U16 | U17 | U18 |

|    | V2 | V3 | V4 | V5 | V6 | V7 | V8 | V9 | V10 | V11 | V12 | V13 | V14 | V15 | V16 | V17 |     |

Figure 2.1 Pin Assignment (P-FBGA281)

The following provides a pin cross reference by pin number.

Table 2.1 Pin Cross Reference by Pin Number (1/2)

|            |           |            |           |            |             | -          | ,           |            |                 |

|------------|-----------|------------|-----------|------------|-------------|------------|-------------|------------|-----------------|

| Pin<br>No. | Pin Name  | Pin<br>No. | Pin Name  | Pin<br>No. | Pin Name    | Pin<br>No. | Pin Name    | Pin<br>No. | Pin Name        |

| A1         | NC        | A13        | PK1/KEY1  | B8         | P75/AIN5    | C2         | PCST3 (DSU) | C14        | PK6/KEY6        |

| A2         | VREFL     | A14        | PI1/INT1  | B9         | PL0/TA4IN   | C3         | P92/AIN18   | C15        | PI5/INT9        |

| A3         | P90/AIN16 | A15        | PI3/INT3  | B10        | PL3/TAAIN   | C4         | P95/AIN21   | C16        | TCK (JTAG)      |

| A4         | P93/AIN19 | A16        | PI6/INTA  | B11        | PM1         | C5         | P82/AIN10   | C17        | CVCC2           |

| A5         | P80/AIN8  | A17        | X2        | B12        | PM4         | C6         | P85/AIN13   | C18        | XT2             |

| A6         | P83/AIN11 | B1         | AVCC31    | B13        | PK2/KEY2    | C7         | P72/AIN2    | D1         | SDAO/TPC (DSU)  |

| A7         | P70/AIN0  | B2         | VREFH     | B14        | PI2/INT2    | C8         | AVSS        | D2         | PCST2 (DSU)     |

| A8         | P74/AIN4  | B3         | P91/AIN17 | B15        | PI4/INT4    | C9         | PL1/TA6IN   | D3         | SDI/ DINT (DSU) |

| A9         | NC        | B4         | P94/AIN20 | B16        | PI7         | C10        | PL4/TB0IN0  | D4         | DVCC2           |

| A10        | PL2/TA8IN | B5         | P81/AIN9  | B17        | CVSS        | C11        | PM2         | D5         | P96/AIN22       |

| A11        | PM0       | B6         | P84/AIN12 | B18        | X1          | C12        | PM5         | D6         | P86/AIN14       |

| A12        | PK0/KEY0  | B7         | P71/AIN1  | C1         | PCST0 (DSU) | C13        | PK3/KEY3    | D7         | P73/AIN3        |

| Pin<br>No. | Pin Name    | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        |

|------------|-------------|------------|-----------------|------------|-----------------|------------|-----------------|------------|-----------------|

| D8         | DVCC2       | F18        | P44/SCOUT       | K14        | P12/D10/AD10    | N18        | DVSS            | T8         | PD4/TXD4        |

| D9         | DVSS        | G1         | RESET           | K15        | P13/D11/AD11    | P1         | PP0             | Т9         | PC0/TXD0        |

| D10        | PL5/TB0IN1  | G2         | TEST5           | K16        | P14/D12/AD12    | P2         | PB2/TB2IN0/INT5 | T10        | PC3/TXD1        |

| D11        | PM3         | G3         | FVCC2           | K17        | DVCC33          | P3         | PB3/TB2IN1/INT6 | T11        | PH4/TCOUT4      |

| D12        | PM6         | G4         | FVSS            | K18        | P15/D13/AD13    | P4         | PB4/TB2OUT      | T12        | PE2/SCLK5/ CTS5 |

| D13        | PK4/KEY4    | G5         | PJ0/INT0        | L1         | FVCC3           | P5         | PB5/TB3IN0/INT7 | T13        | PE5/KEYB        |

| D14        | PK7/KEY7    | G6         | BW0             | L2         | PO1             | P6         | PG5/TC5IN       | T14        | P53/A3          |

| D15        | DVCC34      | G13        | TRST            | L3         | PO2             | P7         | PG7/TC7IN       | T15        | P56/A6          |

| D16        | TDI (JTAG)  | G14        | CAP1            | L4         | PO3             | P8         | PD6/SCLK4/ CTS4 | T16        | P62/A10         |

| D17        | TDO (JTAG)  | G15        | P41/CS1         | L5         | PO4             | P9         | PC2/SCLK0/ CTS0 | T17        | P65/A13         |

| D18        | XT1         | G16        | P37/ALE         | L6         | PO7             | P10        | PC5/SCLK1/ CTS1 | T18        | P20/A16/A0      |

| E1         | DCLK (DSU)  | G17        | P35/BUSAK       | L13        | TEST3           | P11        | PH6/TCOUT6      | U1         | PA0/TA0IN       |

| E2         | PCST1 (DSU) | G18        | FVCC2           | L14        | P06/D6/AD6      | P12        | NC              | U2         | PA3/TA3OUT      |

| E3         | DBGE        | H1         | NMI             | L15        | FVCC2           | P13        | P50/A0          | U3         | PA6/TA9OUT      |

| E4         | PJ3/INTLV   | H2         | DVCC31          | L16        | P07/D7/AD7      | P14        | P51/A1          | U4         | PF1/SI/SCL      |

| E5         | PJ4/ENDIAN  | H3         | PN7             | L17        | P10/D8/AD8      | P15        | P54/A4          | U5         | PF5/DREQ3       |

| E6         | P97/AIN23   | H4         | BW1             | L18        | P11/D9/AD9      | P16        | P23/A19/A3      | U6         | PG2/TC2IN       |

| E7         | P87/AIN15   | H5         | PLLOFF          | M1         | PO0             | P17        | P24/A20/A4      | U7         | PD2/RXD3        |

| E8         | P76/AIN6    | H6         | TEST1           | M2         | PP5             | P18        | P25/A21/A5      | U8         | DVCC32          |

| E9         | P77/AIN7    | H13        | TEST2           | M3         | PP6             | R1         | PB0/TB0OUT      | U9         | PC7/RXD2        |

| E10        | PL6/TB1IN0  | H14        | P31/ WR         | M4         | PP7             | R2         | PB1/TB1OUT      | U10        | PH1/TCOUT1      |

| E11        | PL7/TB1IN1  | H15        | P32/HWR         | M5         | PB7/TB3OUT      | R3         | PF3/ DREQ2      | U11        | PH3/TCOUT3      |

| E12        | PM7         | H16        | P33/WAIT/RDY    | M6         | DVCC32          | R4         | PF4/ DACK2      | U12        | PE1/RXD5        |

| E13        | PK5/KEY5    | H17        | P30/ RD         | M13        | TEST4           | R5         | PF7/TBTIN       | U13        | PE4/KEYA        |

| E14        | NC          | H18        | P40/ CS0        | M14        | P02/D2/AD2      | R6         | PG4/TC4IN       | U14        | DVCC32          |

| E15        | TMS (JTAG)  | J1         | PN2/SCLK6/ CTS6 | M15        | FVSS            | R7         | PG6/TC6IN       | U15        | P57/A7          |

| E16        | CVCCH       | J2         | PN3             | M16        | P03/D3/AD3      | R8         | PD5/RXD4        | U16        | P63/A11         |

| E17        | NC          | J3         | PN4             | M17        | P04/D4/AD4      | R9         | PC1/RXD0        | U17        | P66/A14         |

| E18        | DVCC2       | J4         | PN5             | M18        | P05/D5/AD5      | R10        | PC4/RXD1        | U18        | DVCC33          |

| F1         | DVSS        | J5         | PN6             | N1         | PP1             | R11        | PH5/TCOUT5      | V2         | PA2/TA2IN       |

| F2         | DRESET      | J6         | DVCC2           | N2         | PP2             | R12        | PH7/TCOUT7      | V3         | PA5/TA7OUT      |

| F3         | SYSRDY      | J13        | FVSS            | N3         | PP3             | R13        | PE6/KEYC        | V4         | PF0/SO/SDA      |

| F4         | PJ1/BUSMD   | J14        | P16/D14/AD14    | N4         | PP4             | R14        | P52/A2          | V5         | PG0/TC0IN       |

| F5         | PJ2/BOOT    | J15        | DVSS            | N5         | PB6/TB3IN1/INT8 | R15        | P55/A5          | V6         | PG1/TC1IN       |

| F7         | AVSS        | J16        | P17/D15/AD15    | N7         | DVSS            | R16        | P61/A9          | V7         | PD1/TXD3        |

| F8         | AVSS        | J17        | P36/R/W         | N8         | PD7/KEY8        | R17        | P21/A17/A1      | V8         | PD0/SCLK2/ CTS2 |

| F9         | AVCC32      | J18        | P34/BUSRQ       | N9         | DVCC2           | R18        | P22/A18/A2      | V9         | PC6/TXD2        |

| F10        | DVCC34      | K1         | PN0/TXD6        | N10        | DVSS            | T1         | PA1/TA1OUT      | V10        | PH0/TCOUT0      |

| F11        | PI0/ ADTRG  | K2         | PN1/RXD6        | N11        | RSTPUP          | T2         | PA4/TA5OUT      | V11        | PH2/TCOUT2      |

| F12        | DVSS        | K3         | PO5             | N12        | DVSS            | Т3         | PA7/TABOUT      | V12        | PE0/TXD5        |

| F14        | CAP2        | K4         | PO6             | N14        | P26/A22/A6      | T4         | PF2/SCK         | V13        | PE3/KEY9        |

| F15        | P42/ CS2    | K5         | FVSS            | N15        | P27/A23/A7      | T5         | PF6/ DACK3      | V14        | PE7/KEYD        |

| F16        | P43/ CS3    | K6         | DVSS            | N16        | P00/D0/AD0      | T6         | PG3/TC3IN       | V15        | P60/A8          |

| F17        | DVCC33      | K13        | TEST0           | N17        | P01/D1/AD1      | T7         | PD3/SCLK3/ CTS3 | V16        | P64/A12         |

|            |             |            |                 | · · · · ·  |                 |            | ·               | V17        | P67/A15         |

Table 2.1 Pin Cross Reference by Pin Number (2/2)

# 2.2 Pin Usage Information

Table 2.2 lists input and output pins of the TMP1962F10AXBG.

# Table 2.2 Pin Names and Function (1/6)

| Pin Name         | # of<br>Pins | Туре         | Function                                                                                |

|------------------|--------------|--------------|-----------------------------------------------------------------------------------------|

| P00-P07          | 8            | Input/Output | Port 0: Individually programmable input or output                                       |

| D0-D7            |              | Input/Output | Data (Lower): Bits 0-7 of the data bus (separate bus mode)                              |

| AD0-D7           |              | Input/Output | Address /Data (Lower): Bits 0-7 of the address/data bus (multiplex bus mode)            |

| P10-P17          | 8            | Input/Output | Port 1: Individually programmable input or output                                       |

| D8-D15           |              | Input/Output | Data (Upper): Bits 8-15 of the data bus (separate bus mode)                             |

| AD8-AD15         |              | Input/Output | Address /Data (Upper): Bits 8-15 of the address/data bus (multiplex bus mode)           |

| A8-A15           |              | Output       | Address: Bits 8-15 of the address bus (multiplex bus mode)                              |

| P20-P27          | 8            | Input/Output | Port 2: Individually programmable input or output                                       |

| A16-A23          |              | Output       | Address: Bit 15-23 of the address bus (separate bus mode)                               |

| A0-A7            |              | Output       | Address: Bit 0-7 of the address bus (multiplex bus mode)                                |

| A16-A23          |              | Output       | Address: Bit 16-23 of the address bus (multiplex bus mode)                              |

| P30              | 1            | Output       | Port 30: Output-only                                                                    |

| RD               |              | Output       | Read Strobe: Asserted during a read operation from an external memory device            |

| P31              | 1            | Output       | Port 31: Output-only                                                                    |

| WR               |              | Output       | Write Strobe: Asserted during a write operation on D0-D7                                |

| P32              | 1            | Input/Output | Port 32: Programmable as input or output (with internal pull-up register)               |

| HWR              |              | Output       | Higher Write Strobe: Asserted during a write operation on D8-D15                        |

| P33              | 1            | Input/Output | Port 33: Programmable as input or output (with internal pull-up resister)               |

| WAIT             |              | Input        | Wait: Causes the CPU to suspend external bus activity                                   |

| RDY              |              | Input        | Ready: Informs the CPU of bus ready condition                                           |

| P34              | 1            | Input/Output | Port 34: Programmable as input or output (with internal pull-up resister)               |

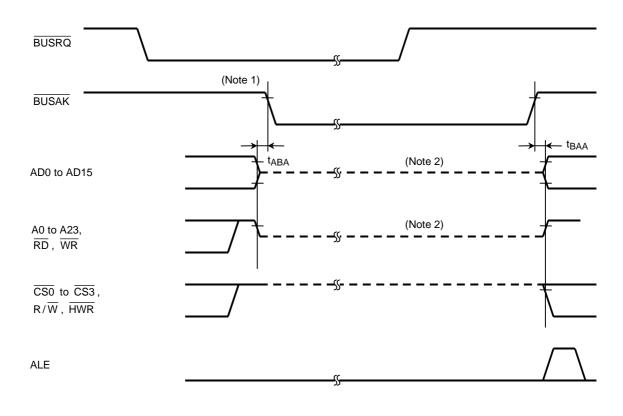

| BUSRQ            |              | Input        | Bus Request: Asserted by an external bus master to request bus mastership               |

| P35              | 1            | Input/Output | Port 35: Programmable as input or output (with internal pull-up resister)               |

| BUSAK            |              | Output       | Bus Acknowledge: Indicates that the CPU has relinquished the bus in response to         |

| 200, 11          |              | Output       | BUSRQ .                                                                                 |

| P36              | 1            | Input/Output | Port 36: Programmable as input or output (with internal pull-up resister)               |

| $R/\overline{W}$ |              | Output       | Read/Write: Indicates the direction of data transfer on the bus: 1 = read or dummy      |

|                  |              |              | cycle, 0 = write cycle                                                                  |

| P37              | 1            | Input/Output | Port 37: Programmable as input or output                                                |

| ALE              |              | Output       | Address Latch Enable (This signal is driven out only when external memory is accessed.) |

| P40              | 1            | Input/Output | Port 40: Programmable as input or output (with internal pull-up resister)               |

| CS0              |              | Output       | Chip Select 0: Asserted low to enable external devices at programmed addresses          |

| P41              | 1            | Input/Output | Port 41: Programmable as input or output (with internal pull-up resister)               |

| CS1              |              | Output       | Chip Select 1: Asserted low to enable external devices at programmed addresses          |

| P42              | 1            | Input/Output | Port 42: Programmable as input or output (with internal pull-up resister)               |

| CS2              |              | Output       | Chip Select 2: Asserted low to enable external devices at programmed addresses          |

| P43              | 1            | Input/Output | Port 43: Programmable as input or output (with internal pull-up resister)               |

| CS3              |              | Output       | Chip Select 3: Asserted low to enable external devices at programmed addresses          |

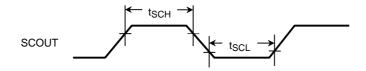

| P44              | 1            | Input/Output | Port 44: Programmable as input or output                                                |

| SCOUT            |              | Output       | System Clock Output: Drives out a clock signal at the frequency equal to or one half of |

|                  |              |              | CPU clock (high-speed or low-speed)                                                     |

| P50-P57          | 8            | Input/Output | Port 5: Individually programmable as input or output                                    |

| A0-A7            |              | Output       | Address: Address bus 0-7 (separate bus mode)                                            |

| P60-P67          | 8            | Input/Output | Port 6: Individually programmable as input or output                                    |

| A8-A15           |              | Output       | Address: Address bus 8-15 (separate bus mode)                                           |

| P70-P77          | 8            | Input        | Port 7: Input-only                                                                      |

| AN0-AN7          |              | Input        | Analog Input: Input to the on-chip A/D converter                                        |

| P80-P87          | 8            | Input        | Port 8: Input-only                                                                      |

| AN8-AN15         |              | Input        | Analog Input: Input to the on-chip A/D converter                                        |

| Table 2.2 Pin Names and | I Function | (2/6) |

|-------------------------|------------|-------|

|-------------------------|------------|-------|

| Pin Name      | # of<br>Pins | Туре                  | Function                                                                                                                   |

|---------------|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| P90-P97       | 8            | Input                 | Port 9: Input-only                                                                                                         |

| AN16-AN23     |              | Input                 | Analog Input: Input to the on-chip A/D converter                                                                           |

| PI0           | 1            | Input/Output          | Port I0: Programmable as input or output                                                                                   |

| ADTRG         |              | Input                 | AD Trigger: Starts an A/D conversion                                                                                       |

|               |              |                       | Schmitt trigger input                                                                                                      |

| PI1           | 1            | Input/Output          | Port I1: Programmable as input or output                                                                                   |

| INT1          |              | Input                 | Interrupt Request 1: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                       |

|               |              |                       | Schmitt trigger input                                                                                                      |

| PI2           | 1            | Input/Output          | Port I2: Programmable as input or output                                                                                   |

| INT2          |              | Input                 | Interrupt Request 2: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                       |

|               |              |                       | Schmitt trigger input                                                                                                      |

| PI3           | 1            | Input/Output          | Port I3: Programmable as input or output                                                                                   |

| INT3          |              | Input                 | Interrupt Request 3: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive Schmitt trigger input |

| Pl4           | 1            | Input/Output          | Port I4: Programmable as input or output                                                                                   |

| INT4          | 1            | Input                 | Interrupt Request 4: Programmable to be high-level, low-level, rising-edge or                                              |

|               |              | mput                  | falling-edge sensitive                                                                                                     |

|               |              |                       | Schmitt trigger input                                                                                                      |

| PI5           | 1            | Input/Output          | Port I5: Programmable as input or output                                                                                   |

| INT9          |              | Input                 | Interrupt Request 9: Programmable to be high-level, low-level, rising-edge or                                              |

|               |              |                       | falling-edge sensitive                                                                                                     |

|               |              |                       | Schmitt trigger input                                                                                                      |

| PI6           | 1            | Input/Output          | Port I6: Programmable as input or output                                                                                   |

| INTA          |              | Input                 | Interrupt Request A: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                       |

|               |              |                       | Schmitt trigger input                                                                                                      |

| PI7           | 1            | Input/Output          | Port I7: Programmable as input or output                                                                                   |

| PA0           | 1            | Input/Output          | Port A0: Programmable as input or output                                                                                   |

| TAOIN         |              | Input                 | 8-Bit Timer 0 Input: Input to 8-bit Timer 0                                                                                |

| PA1           | 1            | Input/Output          | Port A1: Programmable as input or output                                                                                   |

| TA1OUT        |              | Output                | 8-Bit Timer 01 Output: Output from either 8-bit Timer 0 or Timer 1                                                         |

| PA2           | 1            | Input/Output          | Port A2: Programmable as input or output                                                                                   |

| TA2IN         |              | Input                 | 8-Bit Timer 2 Input: Input to 8-bit Timer 2                                                                                |

| PA3           | 1            | Input/Output          | Port A3: Programmable as input or output                                                                                   |

| TA3OUT        |              | Output                | 8-Bit Timer 23 Output: Output from either 8-bit Timer 2 or Timer 3                                                         |

| PA4           | 1            | Input/Output          | Port A4: Programmable as input or output                                                                                   |

| TA5OUT        | 4            | Output                | 8-Bit Timer 45 Output: Output from either 8-bit Timer 4 or Timer 5                                                         |

| PA5           | 1            | Input/Output          | Port A5: Programmable as input or output                                                                                   |

| TA7OUT        | 4            | Output                | 8-Bit Timer 67 Output: Output from either 8-bit Timer 6 or Timer 7                                                         |

| PA6<br>TA9OUT | 1            | Input/Output<br>Input | Port A6: Programmable as input or output<br>8-Bit Timer 89 Output: Output from either 8-bit Timer 8 or Timer 9             |

| PA7           | 1            | Input/Output          | Port A7: Programmable as input or output                                                                                   |

| TABOUT        | 1            | Output                | 8-Bit Timer AB Output: Output from either 8-bit Timer A or Timer B                                                         |

| PB0           | 1            | Input/Output          | Port B0: Programmable as input or output                                                                                   |

| TBOOUT        |              | Output                | 16-Bit Timer 0 Output: Output from 16-bit Timer 0                                                                          |

| PB1           | 1            | Input/Output          | Port B1: Programmable as input or output                                                                                   |

| TB1OUT        |              | Output                | 16-Bit Timer 1 Output: Output from 16-bit Timer 1                                                                          |

| PB2           | 1            | Input/Output          | Port B2: Programmable as input or output                                                                                   |

| TB2IN0        |              | Input                 | 16-Bit Timer 2 Input 0: Count/capture trigger input to 16-bit Timer 2                                                      |

| INT5          |              | Input                 | Interrupt Request 5: Programmable to be high-level, low-level, rising-edge or                                              |

| -             |              |                       | falling-edge sensitive                                                                                                     |

| Table 2.2 | Pin Names and Function (3/6) |  |

|-----------|------------------------------|--|

|-----------|------------------------------|--|

| Pin Name              | # of<br>Pins | Туре                           | Function                                                                                                                                                                                                               |

|-----------------------|--------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB3<br>TB2IN1<br>INT6 | 1            | Input/Output<br>Input<br>Input | Port B3: Programmable as input or output<br>16-Bit Timer 2 Input 1: Capture trigger input to 16-bit Timer 2<br>Interrupt Request 6: Programmable to be high-level, low-level, rising-edge or<br>falling-edge sensitive |

| PB4                   | 1            | Input/Output                   | Port B4: Programmable as input or output                                                                                                                                                                               |

| TB2OUT                |              | Output                         | 16-Bit Timer 2 Output: Output from 16-bit Timer 2                                                                                                                                                                      |

| PB5<br>TB3IN0         | 1            | Input/Output                   | Port B5: Programmable as input or output<br>16-Bit Timer 3 Input 0: Count/capture trigger input to 16-bit Timer 3                                                                                                      |

| INT7                  | 1            | Input                          | Interrupt Request 7: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive<br>Port B6: Programmable as input or output                                                                       |

| PB6                   | 1            | Input/Output                   | 16-Bit Timer 3 Input 1: Capture trigger input to 16-bit Timer 3                                                                                                                                                        |

| TB3IN1                |              | Input                          | Interrupt Request 8: Programmable to be high-level, low-level, rising-edge or                                                                                                                                          |

| INT8                  |              | Input                          | falling-edge sensitive                                                                                                                                                                                                 |

| PB7                   | 1            | Input/Output                   | Port B7: Programmable as input or output                                                                                                                                                                               |

| TB3OUT                |              | Output                         | 16-Bit Timer 3 Output: Output from 16-bit Timer 3                                                                                                                                                                      |

| PC0                   | 1            | Input/Output                   | Port C0: Programmable as input or output                                                                                                                                                                               |

| TXD0                  |              | Output                         | Serial Transmit Data 0: Programmable as a push-pull or open-drain output                                                                                                                                               |

| PC1                   | 1            | Input/Output                   | Port C1: Programmable as input or output                                                                                                                                                                               |

| RXD0                  |              | Input                          | Serial Receive Data 0                                                                                                                                                                                                  |

| PC2                   | 1            | Input/Output                   | Port C2: Programmable as input or output                                                                                                                                                                               |

| SCLK0                 |              | Input                          | Serial Clock Input/Output 0                                                                                                                                                                                            |

| CTS0                  |              | Input                          | Serial Clear-to-Send 0                                                                                                                                                                                                 |

| PC3<br>TXD1           | 1            | Input/Output<br>Output         | Programmable as a push-pull or open-drain output<br>Port C3: Programmable as input or output<br>Serial Transmit Data 1: Programmable as a push-pull or open-drain output                                               |

| PC4<br>RXD1           | 1            | Input/Output                   | Port C4: Programmable as input or output<br>Serial Receive Data 1                                                                                                                                                      |

| PC5                   | 1            | Input/Output                   | Port C5: Programmable as input or output                                                                                                                                                                               |

| SCLK1                 |              | Input                          | Serial Clock Input/Output 1                                                                                                                                                                                            |

| CTS1                  |              | Input                          | Serial Clear-to-Send 1                                                                                                                                                                                                 |

| PC6<br>TXD2           | 1            | Input/Output<br>Output         | Programmable as a push-pull or open-drain output<br>Port C6: Programmable as input or output<br>Serial Transmit Data 2: Programmable as a push-pull or open-drain output                                               |

| PC7                   | 1            | Input/Output                   | Port C7: Programmable as input or output                                                                                                                                                                               |

| RXD2                  |              | Input                          | Serial Receive Data 2                                                                                                                                                                                                  |

| PD0<br>SCLK2<br>CTS2  | 1            | Input/Output<br>Input<br>Input | Port D0: Programmable as input or output<br>Serial Clock Input/Output 2<br>Serial Clear-to-Send 2<br>Programmable as a push-pull or open-drain output                                                                  |

| PD1                   | 1            | Input/Output                   | Port D1: Programmable as input or output                                                                                                                                                                               |

| TXD3                  |              | Output                         | Serial Transmit Data 3: Programmable as a push-pull or open-drain output                                                                                                                                               |

| PD2                   | 1            | Input/Output                   | Port D2: Programmable as input or output                                                                                                                                                                               |

| RXD3                  |              | Input                          | Serial Receive Data 3                                                                                                                                                                                                  |

| PD3<br>SCLK3<br>CTS3  | 1            | Input/Output<br>Input<br>Input | Port D3: Programmable as input or output<br>Serial Clock Input/Output 3<br>Serial Clear-to-Send 3<br>Programmable as a push-pull or open-drain output                                                                  |

| PD4                   | 1            | Input/Output                   | Port D4: Programmable as input or output                                                                                                                                                                               |

| TXD4                  |              | Output                         | Serial Transmit Data 4: Programmable as a push-pull or open-drain output                                                                                                                                               |

| PD5                   | 1            | Input/Output                   | Port D5: Programmable as input or output                                                                                                                                                                               |

| RXD4                  |              | Input                          | Serial Receive Data 4                                                                                                                                                                                                  |

| PD6<br>SCLK4<br>CTS4  | 1            | Input/Output<br>Input<br>Input | Port D6: Programmable as input or output<br>Serial Clock Input/Output 4<br>Serial Clear-to-Send 4<br>Programmable as a push-pull or open-drain output                                                                  |

| PD7<br>KEY8           | 1            | Input/Output<br>Input          | Port D7: Programmable as input or output<br>KEY on wake up Input 8: (dynamic pull-up selectable) (with internal pull-up register)<br>Schmitt trigger input                                                             |

| Table 2.2 | Pin Names and Function (4/6) |

|-----------|------------------------------|

|-----------|------------------------------|

| Pin Name    | # of<br>Pins | Туре                                  | Function                                                                              |

|-------------|--------------|---------------------------------------|---------------------------------------------------------------------------------------|

| PE0         | 1            | Input/Output                          | Port E0: Programmable as input or output                                              |

| TXD5        |              | Output                                | Serial Transmit Data 5: Programmable as a push-pull or open-drain output              |

| PE1         | 1            | Input/Output                          | Port E1: Programmable as input or output                                              |

| RXD5        |              | Input                                 | Serial Receive Data 5                                                                 |

| PE2         | 1            | Input/Output                          | Port E2: Programmable as input or output                                              |

| SCLK5       |              | Input                                 | Serial Clock Input/Output 5                                                           |

| CTS5        |              | Input                                 | Serial Clear-to-Send 5                                                                |

|             |              |                                       | Programmable as a push-pull or open-drain output                                      |

| PE3         | 1            | Input/Output                          | Port E3: Programmable as input or output                                              |

| KEY9        |              | Input                                 | KEY on wake up Input 9: (dynamic pull-up selectable) (with internal pull-up register) |

|             |              |                                       | Schmitt trigger input                                                                 |

| PE4         | 1            | Input/Output                          | Port E4: Programmable as input or output                                              |

| KEYA        |              | Input                                 | KEY on wake up Input A: (dynamic pull-up selectable) (with internal pull-up register) |

|             |              |                                       | Schmitt trigger input                                                                 |

| PE5         | 1            | Input/Output                          | Port E5: Programmable as input or output                                              |

| KEYB        |              | Input                                 | KEY on wake up Input B: (dynamic pull-up selectable) (with internal pull-up register) |

|             |              |                                       | Schmitt trigger input                                                                 |

| PE6         | 1            | Input/Output                          | Port E6: Programmable as input or output                                              |

| KEYC        |              | Input                                 | KEY on wake up Input C: (dynamic pull-up selectable) (with internal pull-up register) |

|             |              |                                       | Schmitt trigger input                                                                 |

| PE7         | 1            | Input/Output                          | Port C7: Programmable as input or output                                              |

| KEYD        |              | Input                                 | KEY on wake up Input D: (dynamic pull-up selectable) (with internal pull-up register) |

|             |              |                                       | Schmitt trigger input                                                                 |

| PF0         | 1            | Input/Output                          | Port F0: Programmable as input or output                                              |

| SO          |              | Output                                | Data transmit pin when the Serial Bus Interface is in SIO mode                        |

| SDA         |              | Input/Output                          | Data transmit/receive pin when the Serial Bus Interface is in I2C mode;               |

|             |              |                                       | programmable as a push-pull or open-drain output<br>Schmitt trigger input             |

| PF1         | 1            | Input/Output                          | Port F1: Programmable as input or output                                              |

| SI          |              | Input                                 | Data receive pin when the Serial Bus Interface is in SIO mode                         |

| SCL         |              | Input/Output                          | Clock input/output pin when the Serial Bus Interface is in I2C mode;                  |

| 00L         |              | mpuroupur                             | programmable as a push-pull or open-drain output                                      |

|             |              |                                       | Schmitt trigger input                                                                 |

| PF2         | 1            | Input/Output                          | Port F2: Programmable as input or output                                              |

| SCK         |              | Input/Output                          | Clock input/output pin when the Serial Bus Interface is in SIO mode                   |

| PF3         | 1            | Input/Output                          | Port F3: Programmable as input or output                                              |

| DREQ2       |              | Input                                 | DMA Request 2: DMA transfer request from an external I/O device to DMAC2              |

| PF4         | 1            | Input/Output                          | Port F4: Programmable as input or output                                              |

| DACK2       |              | Output                                | DMA Acknowledge 2: Acknowledge signal for DMA transfer requested by DREQ2             |

| PF5         | 1            | Input/Output                          | Port F5: Programmable as input or output                                              |

| DREQ3       |              | Input                                 | DMA Request 3: DMA transfer request from an external I/O device to DMAC3              |

| PF6         | 1            | Input/Output                          | Port F6: Programmable as input or output                                              |

| DACK3       |              | Output                                | DMA Acknowledge 3: Acknowledge signal for DMA transfer requested by DREQ3             |

| PF7         | 1            | Input/Output                          | Port F7: Programmable as input or output                                              |

| TBTIN       |              | Input                                 | 32-bit Time-Base Timer Input: Count input to 32-bit time-base Timer                   |

| PG0-PG7     | 8            | Input/Output                          | Port G: Individually programmable as input or output                                  |

| TC0IN-TC7IN |              | Input                                 | 32-Bit Timer Capture Trigger Input                                                    |

| PH0-PH7     | 8            | Input/Output                          | Port H: Individually programmable as input or output                                  |

| TCOUT0-TCO  |              | Output                                | 32-Bit Timer Compare Match Output                                                     |

| UT7         |              | · · · · · · · · · · · · · · · · · · · |                                                                                       |

| PJ0         | 1            | Input/Output                          | Port J0: Programmable as input or output                                              |

| INT0        |              | Input                                 | Interrupt Request 0: Programmable to be high-level, low-level, rising-edge or         |

|             |              |                                       | falling-edge sensitive                                                                |

|             |              |                                       | Schmitt trigger input                                                                 |

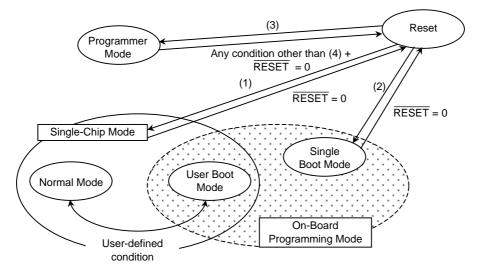

| PJ1<br>BUSMD         1         Input/Output<br>Input         Port 11: Programmable as input or output           BUSMD         Input         External Bus Mode If this pin is sampled high (DVCC21) at the rising edge of RESET,<br>the TMP1962710XASG enters multiplex to smode. If this pin is sampled how at the<br>rising edge of RESET, the TMP1962710XASG enters septerate bus mode. Outring a<br>reset sequence, this pin is sampled high (DVCC21) at the rising edge of RESET, the<br>TMP1962710XASG enters Single Boot Mode If this pin is sampled high (DVCC21) at the rising edge of RESET, the<br>TMP1962710XASG enters Single Boot Mode During a reset sequence, this pin is<br>sampled high (DVCC21) at the rising edge of RESET, the<br>TMP1962710XASG enters NORMAL mode. During a reset sequence, this pin should<br>be pulled up to a logic 1 commonly.           PJ3         1         Input/Output         Port 3: Programmable as input or output           INTLV         1         Input/Output         Port 3: Programmable as input or output           INTLV         1         Input/Output         Port 4: Programmable as input or output           INTLV         1         Input/Output         Port 4: Programmable as input or output           INTLV         1         Input/Output         Port 4: Programmable as input or output           ENDIAN         1         Input/Output         Port 4: Programmable as input or output           ENDIAN         1         Input/Output         Port 4: Programmable as input or output           EVD-PK7         8         Input/Output                                        | Pin Name  | # of<br>Pins | Туре         | Function                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intervention         Intervention         Proof Section           PJ2         1         Input/Output         Port J2: Programmable as input or output           BOOT         1         Input/Output         Port J2: Programmable as input or output           BOOT         1         Input/Output         Port J2: Programmable as input or output           Single Boot Mode: If this pin is sampled low at the rising edge of RESET, the<br>TMP PoS2T IOAXBG enters Single Boot mode for re-programming of the on-chip flash.<br>If this pin is sampled high (DVCC21) at the rising edge of RESET, the<br>TMP PoS2T IOAXBG enters NGMALL mode. During a reset sequence, this pin should<br>be pulled up to a logic 1           PJ3         1         Input/Output         Port J3: Programmable as input or output           INTLV         1         Input         Single Boot Mode: If this pin is sampled and pin (DVCC21) at the rising edge of RESET. The<br>TMP SSC TIOAXBG enters INTERSET. During a reset sequence, this<br>pin should be pulled up to a logic 1           PJ4         1         Input         This pin is used to set the mode. If this pin is sampled high (DVCC21) at the rising edge of RESET. The TMP 1962F10AXBG enters INTERSET. The TMP 1962F10AXBG enters INTERSET.           PK0-PK7         8         Input/Output         Port IX: Programmable as input or output           FKV-KY7         8         Input/Output         Port IX: Programmable as input or output           FAGIN         1         Input/Output         Port IX: Progr                                                                          | PJ1       | 1            | Input/Output | Port J1: Programmable as input or output                                                                                                                                                                                                         |

| BOOT         Input         Single Boot Mode: If this pin is sampled low at the rising adge of RESET, the<br>TMP1962F10AXBG enters NGRMAL mode for re-programming of the on-chip flash.<br>If this pin is sampled high (DVCC21) at the rising adge of RESET, the<br>TMP1962F10AXBG enters NORMAL mode During a reset sequence, this pin is<br>sampled high (DVCC21) at the rising adge of RESET. The<br>instruction of the sampled high (DVCC21) at the rising adge of RESET. The<br>instruction of the sampled high (DVCC21) at the rising adge of RESET. During a reset sequence, this<br>pin should be pulled up to a logic 1.           PJ4         1         Input/Output         Port J3: Programmable as input or output           FNDIAN         1         Input/Output         Port J3: Programmable as input or output           This pin is used to set the mode. If this pin is sampled high (DVCC21) at the rising<br>adge of RESET, the TMP1962F10AXBG enters little-endian<br>mode. During a reset sequence, this pin should be pulled up to a logic 1.           PK0-PK7         8         Input/Output         Port IX: Programmable as input or output           TA4IN         1         Input/Output         Port IX: Programmable as input or output           TA4IN         1         Input/Output         Port IX: Programmable as input or output           TA4IN         1         Input/Output         Port IX: Programmable as input or output           TA4IN         1         Input/Output         Port IX: Programmable as input or output           TA4IN         1         Input/Output         Port IX: Progra            | BUSMD     |              | Input        | the TMP1962F10AXBG enters multiplex bus mode. If this pin is sampled low at the rising edge of RESET, the TMP1962F10AXBG enters separate bus mode. During a reset sequence, this pin should be pulled up to a logic 1or pulled down to a logic 0 |

| Pite         TMP1952F10AXBG enters Single Boot mode for re-programming of the on-chip flash.<br>If this pin is sampled high (VCC2) 11 the rising edge of RESET, the<br>TMP1962F10AXBG enters NORMAL mode. During a reset sequence, this pin should<br>be pulled up to a logic 1 commonly.           PJ3         1         Input/Output         Port J3: Programmable as input or output<br>Interleave Mode: The TMP1962F10AXBG enters Interleave mode when this pin is<br>sampled high (VOC21) at the rising edge of RESET. Touring a reset sequence, this<br>pin should be pulled up to a logic 1.           PJ4         1         Input/Output         Port J4: Programmable as input or output           ENDIAN         Input/Output         Port J4: Programmable as input or output           ENDIAN         Input/Output         Port J4: Programmable as input or output           ENDIAN         Input/Output         Port J4: Programmable as input or output           FK0-PK7         8         Input/Output         Port K: Programmable as input or output           KEV0-FK7         8         Input/Output         Port L1: Programmable as input or output           FAIN         Input         Port L1: Programmable as input or output           TA4IN         Input/Output         Port L1: Programmable as input or output           TA4IN         Input/Output         Port L1: Programmable as input or output           TA4IN         Input/Output         Port L1: Programmable as input or output           TA4IN <td>PJ2</td> <td>1</td> <td>Input/Output</td> <td>Port J2: Programmable as input or output</td>                | PJ2       | 1            | Input/Output | Port J2: Programmable as input or output                                                                                                                                                                                                         |

| INTLVInputInterleave Mode: The TMP1962F10AXBG enters Interleave mode when this pin is<br>sampled high (DVCC21) at the rising edge of RESET. During a reset sequence, this<br>pin should be polled up to a logic 1.PJ41Input/OutputPort J&: Programmable as input or outputENDIAN1Input/OutputPort JA: Programmable as input or outputENDIAN1Input/OutputPort JA: Programmable as input or outputENDIAN1Input/OutputPort K: Programmable as input or outputPK0-PK78Input/OutputPort K: Programmable as input or outputKEY0-KEY71InputKey on wake up input 0-7 (dynamic pull-up selectable) (with internal pull-up register)<br>Schnitt trigger inputPL01Input/OutputPort L0: Programmable as input or outputTA4IN1Input8-bit Timer 4 Input: Input to 8-bit Timer 4PL11Input/OutputPort L2: Programmable as input or outputTA4IN1Input8-bit Timer 6 Input: Input to 8-bit Timer 6PL21Input/OutputPort L2: Programmable as input or outputTA4INInput8-bit Timer 6 Input: Input to 8-bit Timer 7PL31Input/OutputPort L2: Programmable as input or outputTA8INInput8-bit Timer 1 Input to 8-bit Timer 8PL31Input/OutputPort L3: Programmable as input or outputTA4INInput8-bit Timer 1 Input to 8-bit Timer 7PL41Input/OutputPort L3: Programmable as input or outputTA4INInput16-bit Ti                                                                                                                                                                                                                                                                                                                                                                       | BOOT      |              | Input        | TMP1962F10AXBG enters Single Boot mode for re-programming of the on-chip flash.<br>If this pin is sampled high (DVCC21) at the rising edge of RESET, the<br>TMP1962F10AXBG enters NORMAL mode. During a reset sequence, this pin should          |

| INTLVInputInterleave Mode: The TMP 1962F10AXBG enters Interleave mode when this pin is<br>sampled high (DVCC21) at the rising edge of RESET. During a reset sequence, this<br>pin should be pulled up to a logic 1.P.J41Input/OutputPort JA: Programmable as input or outputENDIAN1Input/OutputPort JA: Programmable as input or outputENDIAN1Input/OutputPort JA: Programmable as input or outputENDIAN1Input/OutputPort K: Programmable as input or outputPK0-PK78Input/OutputPort K: Programmable as input or outputFK2P-KEY71InputKey on wake up input 0-7 (dynamic pull-up selectable) (with internal pull-up register)<br>schmitt trigger inputPL01Input/OutputPort ID: Programmable as input or outputTA4IN1Input8-bit Timer 6 Input: Input to 8-bit Timer 6PL21Input8-bit Timer 6 Input: Input to 8-bit Timer 6PL31Input/OutputPort L2: Programmable as input or outputTA4IN1Input8-bit Timer 6 Input: Input to 8-bit Timer 6PL41Input/OutputPort L2: Programmable as input or outputTA4INInput8-bit Timer 6 Input: Input to 8-bit Timer 7PL31Input/OutputPort L2: Programmable as input or outputTA4INInput8-bit Timer 6 Input: Input to 8-bit Timer 7PL41Input/OutputPort L2: Programmable as input or outputTA4INInput16-Bit Timer 1 Input Count/capture trigger input to 16-bit Timer 0PL                                                                                                                                                                                                                                                                                                                                                     | PJ3       | 1            | Input/Output | Port J3: Programmable as input or output                                                                                                                                                                                                         |

| ENDIANInputThis pin is used to set the mode. If this pin is sampled high (DVCC21) at the rising<br>edge of RESET, the TMP1962F10AXBG enters Big-endian mode. If this pin is<br>sampled low at the rising edge of RESET, the TMP1962F10AXBG enters Big-endian mode. If this pin is<br>sampled low at the rising edge of RESET, the TMP1962F10AXBG enters Big-endian mode. If this pin is<br>sampled low at the rising edge of RESET, the TMP1962F10AXBG enters Big-endian mode. If this pin is sampled high (DVCC21) at the rising<br>edge of RESET, the TMP1962F10AXBG enters Big-endian mode. Uning a reset sequence, this pin should be pulled up to a logic 1 or pulled down<br>to a logic 0 depending the endian to be used.PK0-PK78Input/Output<br>InputPort K: Programmable as input or output<br>B-bit Timer 4 Input: Input to 8-bit Timer 4PL01Input/Output<br>B-bit Timer 4 Input: Input to 8-bit Timer 4PL11Input/Output<br>B-bit Timer 6 Input: Input to 8-bit Timer 6PL21Input/Output<br>B-bit Timer 8 Input: Input to 8-bit Timer 8PL31Input/Output<br>B-bit Timer 8 Input: Input to 8-bit Timer 8PL31Input/Output<br>B-bit Timer 8 Input: Input to 8-bit Timer APL41Input/Output<br>B-bit Timer 1 Input to 8-bit Timer APL41Input/Output<br>16-Bit Timer 0 Input 1: Capture trigger input to 16-bit Timer 0PL51Input/Output<br>16-Bit Timer 1 Input 0: Count/capture trigger input to 16-bit Timer 0PL61Input/Output<br>16-Bit Timer 1 Input 0: Count/capture trigger input to 16-bit Timer 1PL71Input/Output<br>16-Bit Timer 1 Input 0: Count/capture trigger input to 16-bit Timer 1PL71Input/Out                                         | INTLV     |              |              | Interleave Mode: The TMP1962F10AXBG enters Interleave mode when this pin is sampled high (DVCC21) at the rising edge of RESET. During a reset sequence, this                                                                                     |

| edge of RESET, the TMP1962F10AXBG enters Big-endian mode. If this pin is<br>sampled low at the rising edge of RESET, the TMP1962F10AXBG enters Little-endian<br>mode. During a reset sequence, this pin should be pulled up to a logic 1 or pulled<br>do a logic 0 depending the endian to be used.PK0-PK78Input/Output<br>hputPort K: Programmable as input or output<br>Key on wake up input 0-7 (dynamic pull-up selectable) (with internal pull-up register)<br>Schmitt trigger inputPL01Input/Output<br>Bott L: Programmable as input or outputTA4INInput/Output<br>Bott L: Programmable as input or outputTA4INInput/Output<br>Bott L: Programmable as input or outputTA6INInput/Output<br>Bott L: Programmable as input or output </td <td>PJ4</td> <td>1</td> <td>Input/Output</td> <td>Port J4: Programmable as input or output</td> | PJ4       | 1            | Input/Output | Port J4: Programmable as input or output                                                                                                                                                                                                         |

| KEY0-KEY7InputKey on wake up input 0-7 (dynamic pull-up selectable) (with internal pull-up register)<br>Schmitt trigger inputPL01Input/OutputPort L0: Programmable as input or outputTAAINInput8-bit Timer 4 Input to 8-bit Timer 4PL11Input/OutputPort L1: Programmable as input or outputTA6INInput8-bit Timer 6 Input: Input to 8-bit Timer 6PL21Input/OutputPort L2: Programmable as input or outputTA8INInput8-bit Timer 6 Input: Input to 8-bit Timer 6PL31Input/OutputPort L3: Programmable as input or outputTAAINInput8-bit Timer 6 Input: Input to 8-bit Timer APL41Input/OutputPort L3: Programmable as input or outputTB0IN0Input16-Bit Timer 0 Input 0: Count/capture trigger input to 16-bit Timer 0PL51Input/OutputPort L5: Programmable as input or outputTB0IN1Input16-Bit Timer 0 Input 1: Capture trigger input to 16-bit Timer 0PL61Input/OutputPort L6: Programmable as input or outputTB1IN0Input16-Bit Timer 1 Input 1: Capture trigger input to 16-bit Timer 1PL71Input/OutputPort I: Programmable as input or outputTB1N1Input/OutputPort N1: Capture trigger input to 16-bit Timer 1PN0-PM78Input/OutputPort N0: Programmable as input or outputTAS6Input/OutputPort N1: Programmable as input or outputPN11Input/OutputPN21Inpu                                                                                                                                                                                                                                                                                                                                                                                                | ENDIAN    |              | Input        | edge of RESET, the TMP1962F10AXBG enters Big-endian mode. If this pin is sampled low at the rising edge of RESET, the TMP1962F10AXBG enters Little-endian mode. During a reset sequence, this pin should be pulled up to a logic 1or pulled down |

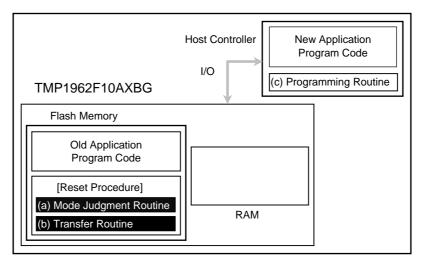

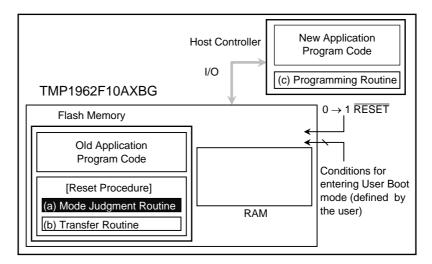

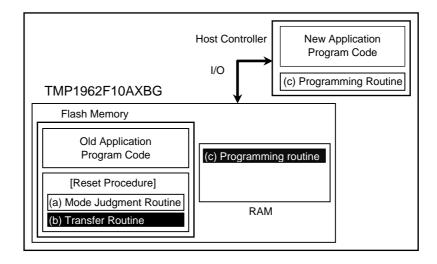

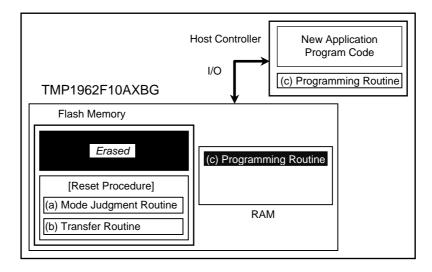

| PL01Input/OutputPort L0: Programmable as input or outputTA4IN1Input8-bit Timer 4 Input: Input to 8-bit Timer 4PL11Input8-bit Timer 4 Input: Input to 8-bit Timer 4PL11Input/OutputPort L1: Programmable as input or outputTA6IN1Input8-bit Timer 6 Input: Input to 8-bit Timer 6PL21Input/OutputPort L2: Programmable as input or outputTA8IN1Input/OutputPL31Input/OutputPL41Input/OutputPL41Input/OutputTAAIN1nput8-bit Timer A Input: Input to 8-bit Timer APL41Input/OutputPL51Input/OutputPL61Input/OutputPL71Input/OutputTB0IN11nput16-Bit Timer 0 Input 0: Count/capture trigger input to 16-bit Timer 0PL51Input/OutputPL71Input/OutputPL71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/OutputPU71Input/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PK0-PK7   | 8            | Input/Output | Port K: Programmable as input or output                                                                                                                                                                                                          |